Serial: 8250/16550 driver, 2 ports, IRQ sharing disabled NFS: Registering the id_resolver key type workingset: timestamp_bits=28 max_order=18 bucket_order=0 futex hash table entries: 512 (order: 3, 32768 bytes) RPC: Registered tcp NFSv4.1 backchannel transport module. RPC: Registered named UNIX socket transport module. UDP-Lite hash table entries: 512 (order: 3, 40960 bytes) UDP hash table entries: 512 (order: 3, 40960 bytes) TCP: Hash tables configured (established 8192 bind 8192) TCP bind hash table entries: 8192 (order: 6, 294912 bytes) TCP established hash table entries: 8192 (order: 3, 32768 bytes) clocksource: Switched to clocksource timer1 supply vcc not found, using dummy regulator

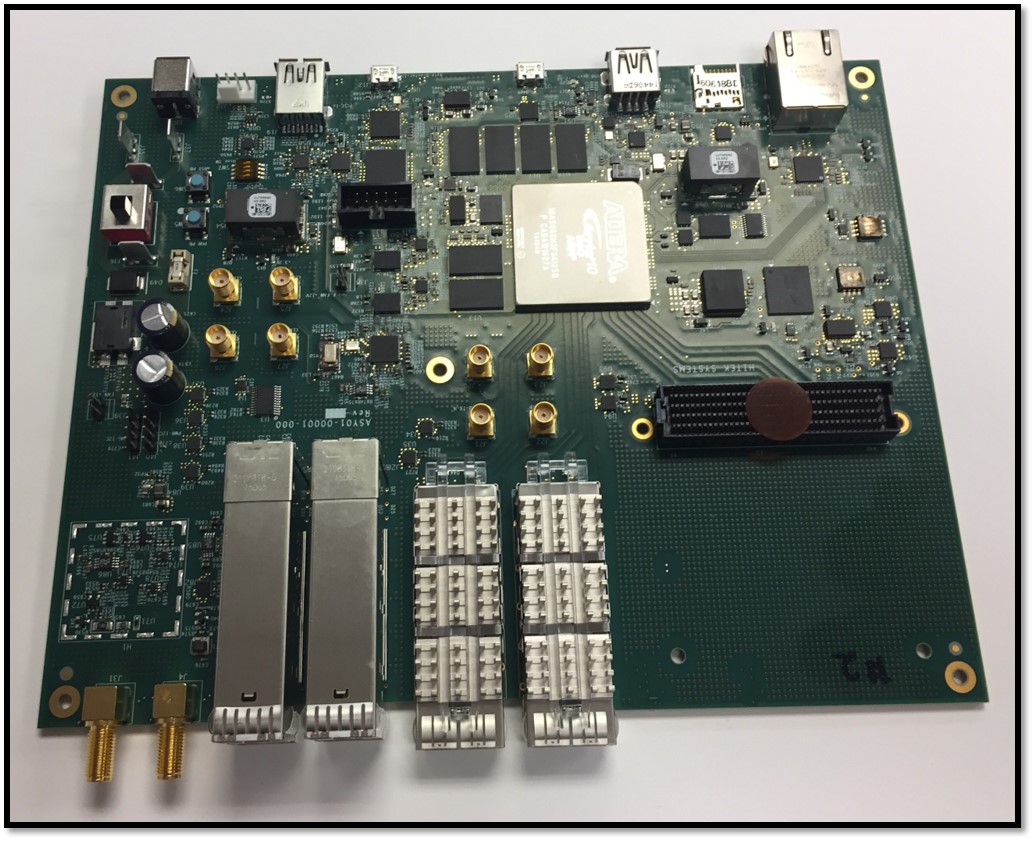

#ARRIA 10 SOC CPUINFO DRIVER#

usbcore: registered new device driver usb usbcore: registered new interface driver hub usbcore: registered new interface driver usbfs hw-breakpoint: maximum watchpoint size is 4 bytes. hw-breakpoint: found 5 (+1 reserved) breakpoint and 1 watchpoint registers. DMA: preallocated 256 KiB pool for atomic coherent allocations clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 19112604462750000 ns VFP support v0.3: implementor 41 architecture 3 part 30 variant 9 rev 4 SMP: Total of 2 processors activated (400.00 BogoMIPS). Setting up static identity map for 0x100000 - 0x100058 ftrace: allocating 21813 entries in 64 pages Mountpoint-cache hash table entries: 2048 (order: 1, 8192 bytes) Mount-cache hash table entries: 2048 (order: 1, 8192 bytes) Calibrating delay loop (skipped), value calculated using timer frequency. per task-struct memory footprint: 1536 bytes memory used by lock dependency info: 5167 kB Lock dependency validator: Copyright (c) 2006 Red Hat, Inc., Ingo Molnar

Switching to timer-based delay loop, resolution 10ns sched_clock: 32 bits at 100MHz, resolution 10ns, wraps every 21474836475ns clocksource: timer1: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 19112604467 ns L2C-310 cache controller enabled, 8 ways, 512 kB

L2C-310 dynamic clock gating enabled, standby mode enabled L2C-310 ID prefetch enabled, offset 1 lines

#ARRIA 10 SOC CPUINFO FULL#

L2C-310: enabling full line of zeros but not enabled in Cortex-A9 L2C-310 enabling early BRESP for Cortex-A9

Build-time adjustment of leaf fanout to 32. SLUB: HWalign=64, Order=0-3, MinObjects=0, CPUs=2, Nodes=1 Inode-cache hash table entries: 65536 (order: 6, 262144 bytes) Dentry cache hash table entries: 131072 (order: 7, 524288 bytes) PID hash table entries: 4096 (order: 2, 16384 bytes) Kernel command line: console=ttyS0,115200 root=/dev/mmcblk0p2 rw rootwait Built 1 zonelists in Zone order, mobility grouping on. CPU: PIPT / VIPT nonaliasing data cache, VIPT aliasing instruction cache CPU: ARMv7 Processor revision 1 (ARMv7), cr=10c5387d Loading Device Tree to 01ff4000, end 01fffffb. Reserving 2048 Bytes for IRQ stack at: ffe386e8įPGA must be in Early Release mode to program core.Ĥ845256 bytes read in 230 ms (20.1 MiB/s) INFO : Skip relocation as SDRAM is non secure memory Once the FPGA has been configured the green D18 LED will turn on and the boot process will continue.

#ARRIA 10 SOC CPUINFO SERIAL#

After turning on the power switch the following messages should appear on the serial console.Ĭonfiguring the FPGA will take a few seconds.

0 kommentar(er)

0 kommentar(er)